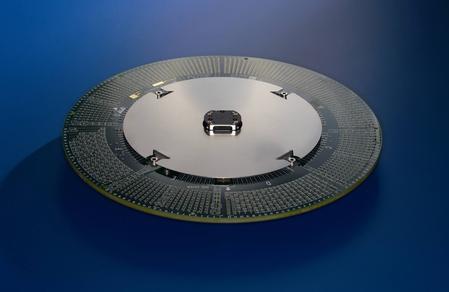

Multitest, a designer and manufacturer of final test handlers, contactors and load boards used by integrated device manufacturers (IDMs) and final test subcontractors worldwide, announces that its UltraFlat™ process meets the requirements of high parallel vertical probe card applications.

For applications such as DDR3 memory, the requirements for the flatness of boards at wafer-level testing become crucial. For optimizing MLO/MLC attachments and contact element interfaces, a better surface is needed. Additionally, flatter PCBs require less compliance from the probe interface and reduce interface wear.

Leveraging the knowledge of PCB stack up engineering and PCB construction, Multitest developed the new “UltraFlat™” process to meet these requirements. UltraFlat™ allows for a very tight overall flatness tolerance to be maintained by removing the bow/twist in the PCB. Unlike “flat-baking” that provides a temporarily flat PCB, Mutltitest’s UltraFlat™ process provides a permanent overall flatness for the PCB.

With UltraFlat™, Multitest typically is able to comply with bow/twist requirements of 1.0 percent.

For more information, please visit www.multitest.com/pcb

Multitest (headquartered in Rosenheim, Germany) is one of the world’s leading manufacturers of test equipment for semiconductors. Multitest markets test handlers, contactors, and ATE printed circuit boards. Globally, more than 700 employees serve the company’s customers in offices and branches in North America, Singapore, Malaysia, the Philippines, Taiwan, China and Thailand.