# Using Physics of Failure to Predict System Level Reliability for Avionic Electronics

IMAPS New England Conference

May 7, 2013

### Agenda

- Introduction

- Avionic Applications

- Common Issues

- Failure Mechanisms

- Virtual Qualification Approach

- Automated Design Analysis Solution

### **Avionic Applications**

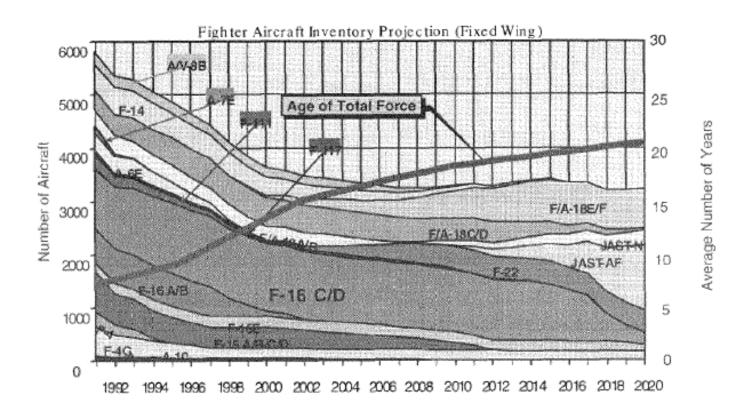

### **Aging Fleet**

### What Do they All Have in Common?

- High Temperature Environments

- Vibration (flight, gunfire) and Shock (Landing)

Environments

- Temperature and Power Cycling Environments

- High Current Flows and Thermal Transfer Requirements

- A variety of materials forming the product

### **Stringent Environmental Conditions**

- Being used at varying temperatures or temperature extremes

- Having a temperature range of -55°C to 125°C

- Being used in an application having a medium to high shock, pressure, vibration, or moisture environment

- Being stored for later usage (over 10 years)

- Having an application life span of greater than 30 years

#### **Failure Mechanisms**

- Thermo-mechanical fatigue induced failures

- CTE mismatch

- Temperature swings

- Bond Wire Fatigue

- Shear Stresses between bond pad and wire

- Repeated flexure of the wire

- Lift off (fast temperature cycling effect)

- Heel Cracking

- Die Attach Fatigue

- Solder Fatigue

- Voids

- Device Burn Out

#### How Can We Resolve these Issues During the Design Phase of a Product?

- Utilize an Automated Design Analysis Approach Because:

- Mil-HBK-217 actuarial in nature

- Physics based algorithms are too time consuming

- Need to shorten NPI cycles and reduce costs

- Increased computing power

- Better way to communicate

### PoF: the Complexity Roadblock

$$au_{HCI} \propto \exp\left[\frac{b_{HCI}}{V_D}\right] \cdot \exp\left[\frac{E_{aHCI}}{kT}\right]$$

$$L = L_{\rm r} \left( \frac{V_r}{V_0} \right) \times 2^{\left( \frac{T_r - T_A}{10} \right)}$$

$$T_f \propto \exp\left(\frac{\sim 0.51 eV}{kT}\right) \times \exp(\sim -0.063\% RH)$$

$$\tau_{TDDB} \propto \exp[-b_{TDDB} \cdot V_G] \cdot \exp[\frac{E_{aTDDB}}{kT}]$$

$$N_{\rm f}^{-0.6}D_{\rm f}^{0.75} + 0.9 \frac{S_{\rm u}}{E} \left[ \frac{\exp(D_{\rm f})}{0.36} \right]^{0.1785\log\frac{10^5}{N_{\rm f}}} - \Delta\epsilon = 0$$

$$\frac{t_1}{t_2} = \left(\frac{V_2}{V_1}\right)^n \exp \frac{E_a}{K_B} \left(\frac{1}{T_1} - \frac{1}{T_2}\right)$$

$$\tau_{EM} \propto (J)^{-n} \cdot \exp\left[\frac{E_{aEM}}{kT}\right]$$

$$\tau_{NBTI} \propto \exp[-b_{NBTI} \cdot V_G] \cdot \exp[\frac{E_{aNBTI}}{kT}]$$

$$(\alpha_2 - \alpha_1) \cdot \Delta T \cdot L = F \cdot \left( \frac{L}{E_1 A_1} + \frac{L}{E_2 A_2} + \frac{h_s}{A_s G_s} + \frac{h_c}{A_c G_c} + \left( \frac{2 - \nu}{9 \cdot G_b a} \right) \right)$$

**DfR Solutions**

#### **Common Failure Modes**

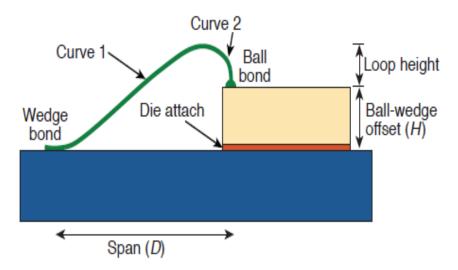

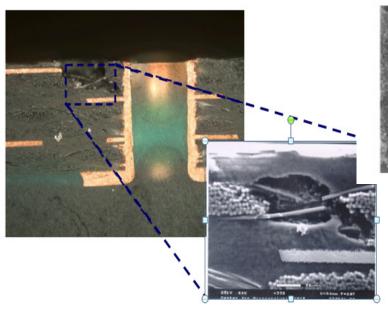

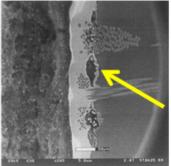

#### o Wire Bonds

Wire bonding has been the most common interconnect for IC packages for over 50 years. The most common materials are gold, aluminum, and more recently copper. The most common bond pad material is aluminum.

Wire bonds tend to fail if exposed to elevated temperatures (intermetallic formation), exposure to elevated temperature and humidity (corrosion) and exposure to temperature cycling (low cycle fatigue).

DfR Solutions

#### **Common Failure Modes: PCBs**

- Printed Wiring Boards have several failure modes that are detrimental to reliable operation. Failures in PCBs can be driven by:

- Size (larger boards tend to experience higher temperatures)

- Thickness (thicker boards experience more thermal stress)

- Material (lower Tg tends to be more susceptible)

- Design (higher density, higher aspect ratios)

- Number of reflow exposures

#### **Common Failure Modes: PCBs**

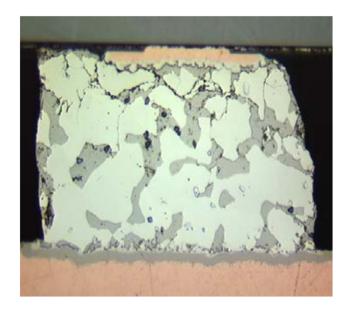

Plated Through Hole Failure Mechanisms: voids (left), etch pits (center) and barrel cracking from fatigue (right)

Conductive anodic filament (CAF), also referred to as metallic electromigration, is an electrochemical process which involves the transport (usually ionic) of a metal across a nonmetallic medium under the influence of an applied electric field. CAF can cause current leakage, intermittent electrical shorts and dielectric breakdown between conductors in printed wiring boards.

PTH voids can cause large stress concentrations, resulting in crack initiation.

Etch pits are due to either insufficient tin resist deposition or improper outer-layer etching process and rework.

Overstress cracking can occur in the PTH due to a Coefficient of Thermal Expansion (CTE) mismatch which places the PTH in compression.

DfR Solutions

#### Common Failure Modes: Solder Fatigue

Thermo-Mechanical Fatigue of solder joints is one of the primary wear-out mechanisms in electronic products. This is especially true in products used outside of commercial/consumer environments where a longer lifetime is required and more severe operating conditions exist. The analysis assesses the fatigue of the solder joints as a function of the stresses applied during its lifetime and provides insight into whether joints are susceptible to failure.

### **Automated Design Analysis Attributes**

- Easy to Utilize

- Easy to Locate commands

- Industry Terminology

- Parts List

- Stack-up

- Pick and Place

- o ODB++

- GERBER

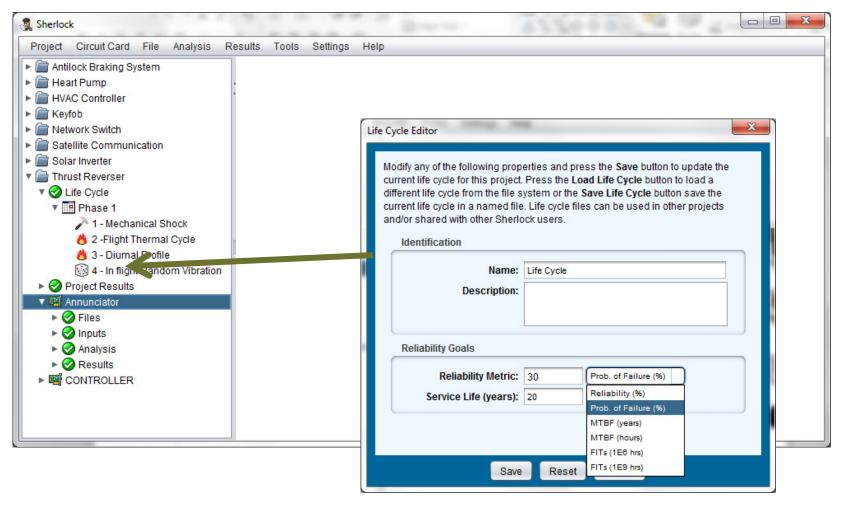

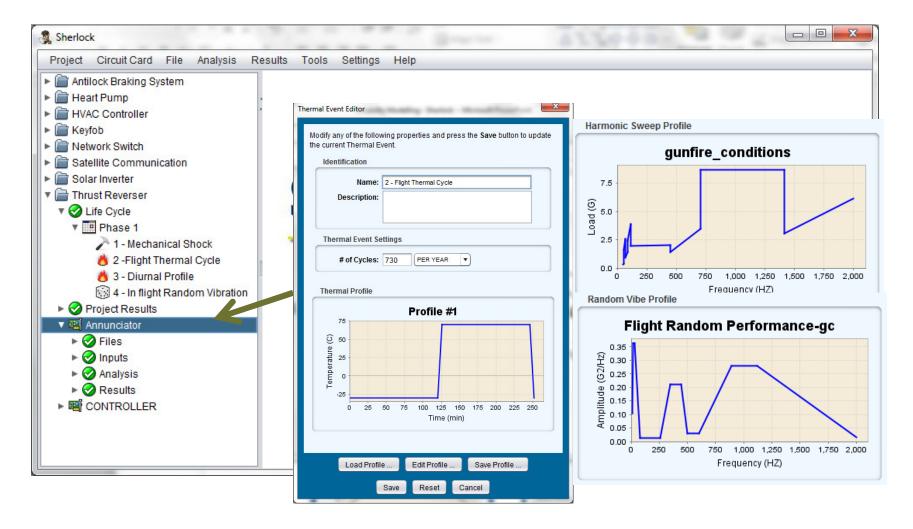

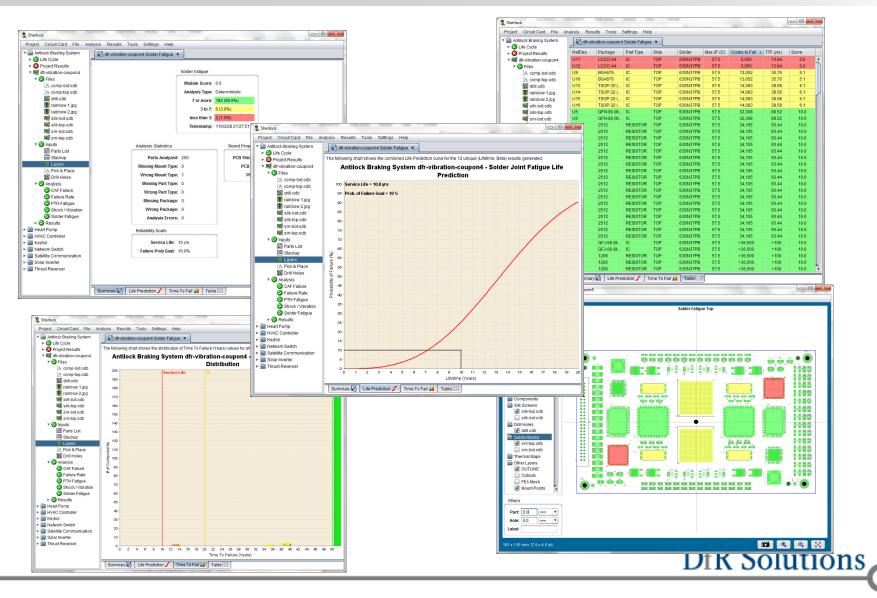

### **Automated Design Analysis**

- There are several high levels steps involved in performing an automated design analysis. They are:

- Define Reliability Goals

- Define Environments

- Add Circuit Cards

- Import Files

- Generate Inputs

- Perform Analysis

- Interpret Results

### **Reliability Goals**

#### **Ambient Environment**

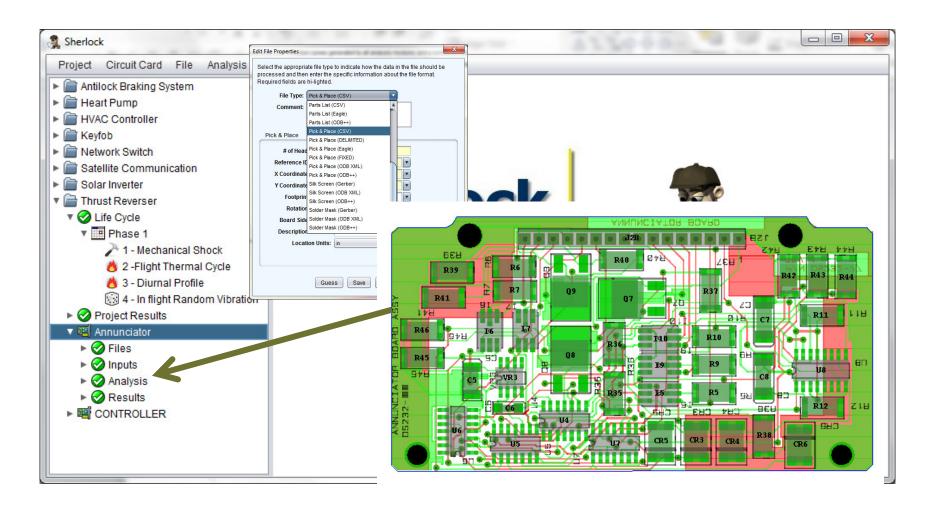

### **Input Design Files**

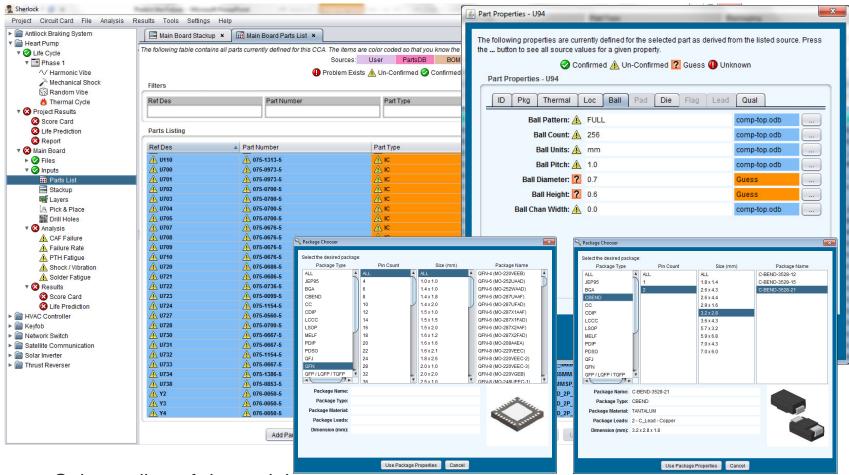

#### **Input: Parts List**

- Color coding of data origin

- Minimizes data entry through intelligent parsing and embedded package and materials database

DfR Solutions

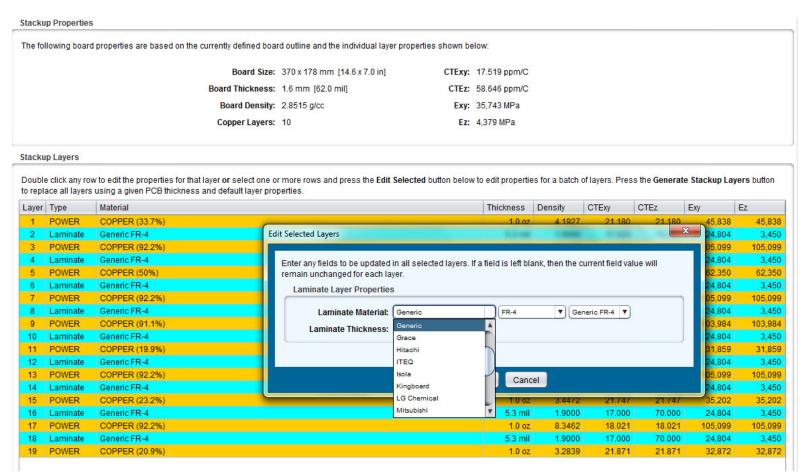

#### Inputs: Stack-Up

- Automatically generates stackup and copper percent (%)

- Embedded database with almost 400 laminate materials with

48 different properties

DfR Solutions

#### **Analyses**

- Eight different analyses can be performed. They are:

- CAF Conductive Anodic Filament Formation

- Plated Through Hole Fatigue

- Solder Joint Fatigue

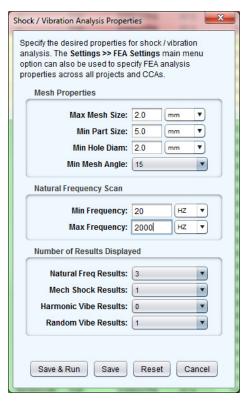

- Finite Element Simulations

- ICT Impact

- DFMEA

- Vibration Fatigue Natural Frequencies

- Mechanical Shock

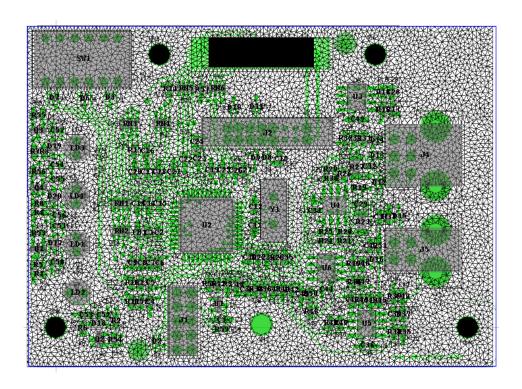

#### **Results: Automated Mesh Generation**

- Identifies optimum mesh density based on board size

- Expert user no longer required; model time reduced by 90%

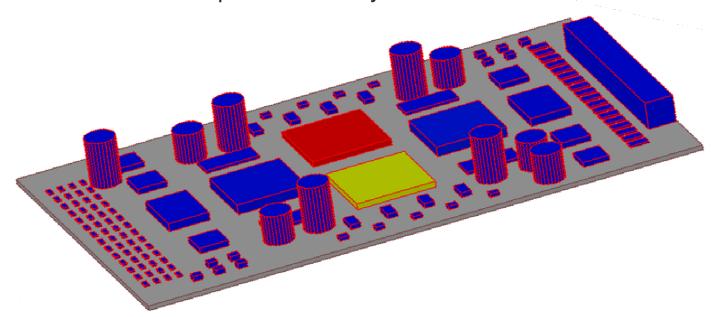

### **3D Output**

The analysis can also establish 3D models by creating a mesh structure and the model from the data input to the analysis.

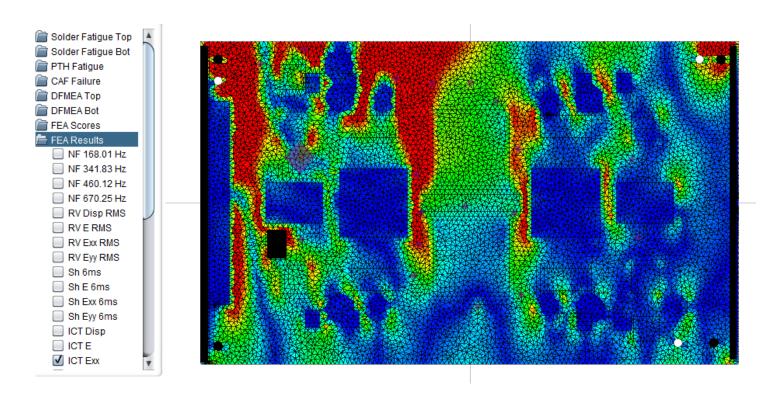

#### **In-Circuit Test Evaluation**

Uses embedded FEA engine to compute board deflection and strain cause by ICT fixture

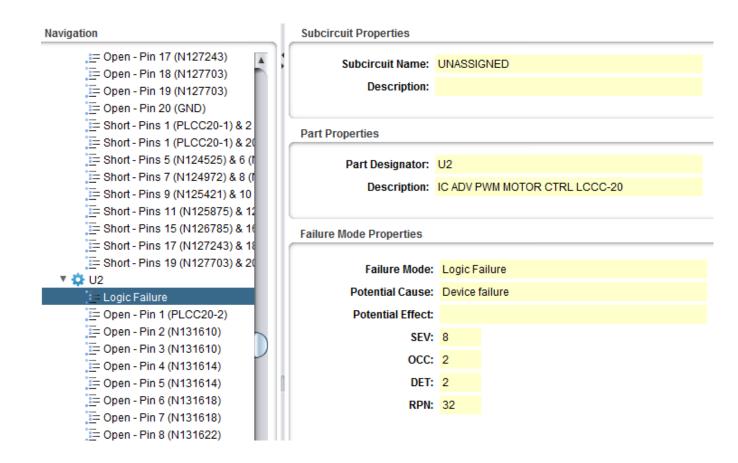

#### **DFMEA**

- Uses ODB++ data including net list to create board level DFMFA

- Includes customizable spreadsheets for export

### **Results: Five Different Outputs**

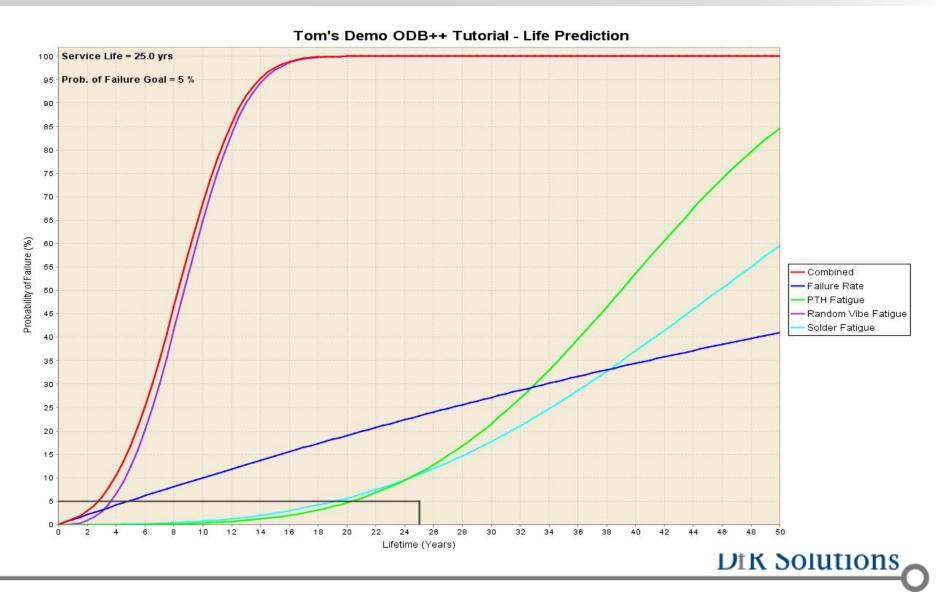

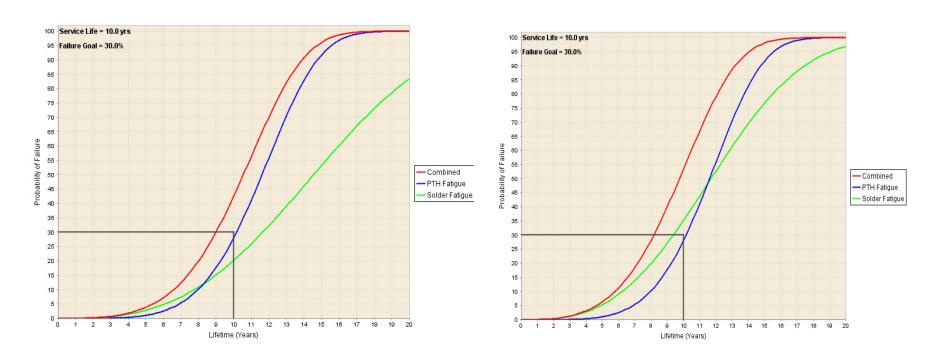

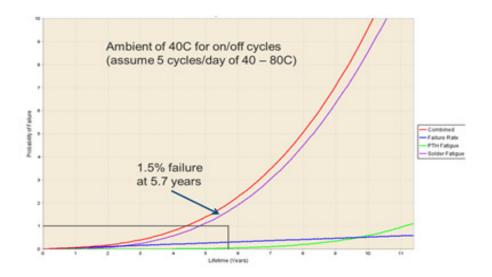

### **Unreliability Curves**

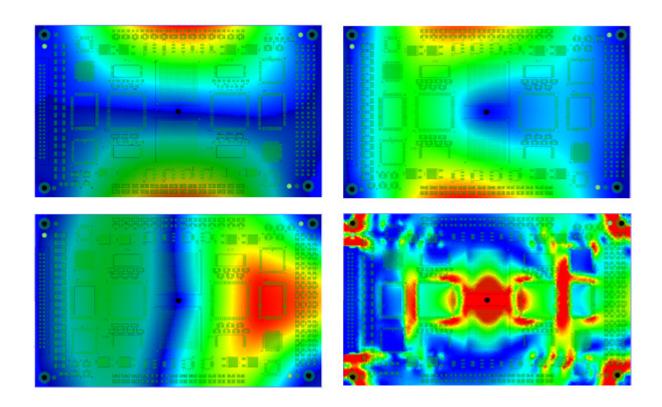

### **Natural Frequencies**

Natural Frequencies Identified (1<sup>st</sup>-upper left), (2<sup>nd</sup>-upper right), (3<sup>rd</sup> -lower left) and 4<sup>th</sup> – lower right)

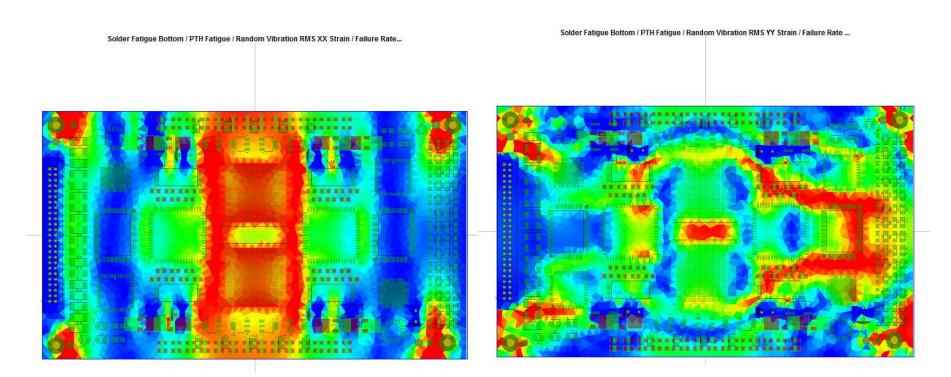

#### **Vibration Strain Levels**

In addition, the analysis can provide data regarding the strains applied to the circuit board as a function of the vibration stress levels. The left illustrates this data in the XX direction and YY in the right image.

#### What If?

#### Comparison of Sn/Pb (left) and SAC305 (right) with respect to solder fatigue

#### **Product Test Plans**

- Product test plans, also known as design verification, product qualification, and accelerated life testing (though, these are not the same thing), are critical to the successful launch of a new product or new technology into the marketplace.

- These test plans require sufficient stresses to bring out real design deficiencies or defects, but not excessive levels that induce non-representative product failure.

- Tests must be rapid enough to meet tight schedules, but not so accelerated as to produce excessive stresses.

- Every test must provide value and must demonstrate correlation to the eventual use environment (which includes screening, storage, transportation/shipping, installation, and operation).

## Thank You!

Greg Caswell

Sr. Member of the Technical Staff

DfR Solutions

301-474-0607 (office)

443-834-9284 (cell)

gcaswell@dfrsolutions.com