Stencil Design Guidelines

DOC#: 010

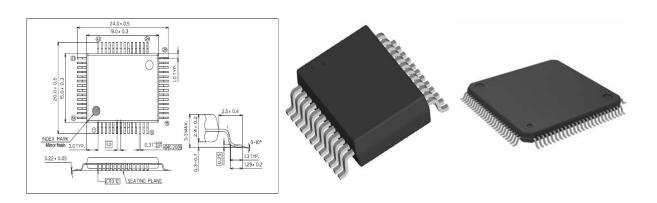

#### Leaded IC's

| Device                                           | Aperture Length                | Aperture Width                                              | Comments or<br>Recommendations   | Stencil<br>Thick. |

|--------------------------------------------------|--------------------------------|-------------------------------------------------------------|----------------------------------|-------------------|

| Leaded component<br>> 50 mil (Standard<br>Pitch) | 1:1 Oblong or ¼ Radius corners | Min of 12 mil gap between apertures recommended             |                                  | Any               |

| Leaded component<br>31 mil (Fine Pitch)          | 1:1 Oblong or ¼ Radius corners | Max. aperture width = 19 mil<br>Min. aperture width > 9 mil |                                  | 5, 6 mil          |

| Leaded component<br>25 mil (Fine Pitch)          | 1:1 Oblong or ¼ Radius corners | Max. aperture width = 14 mil<br>Min. aperture width > 9 mil |                                  | 5, 6 mil          |

| Leaded component<br>20 mil (Fine Pitch)          | 1:1 Oblong or ¼ Radius corners | Max. aperture width=11 mil<br>Min. aperture width > 8 mil   |                                  | 5 mil             |

| Leaded component<br>16 mil,                      | 1:1 Oblong                     | Max. aperture width = 8<br>Min. aperture width > 7          | FG or Eform stencils recommended | 3, 4 mil          |

Common issues with bridging are not selecting the proper stencil thickness and proper stencil reductions. One more item to check is the solder mask resist. Make sure the solder mask is overlaid against the paste mask to check for proper solder resist. Without any solder resists there are more chance of solder flowing or spreading on the PCB which results in bridging.

Note: if there are no solder resist, more reduction may required.

Stencil Design Guidelines

DOC#: 010

REV: 1 PAGE: 2 OF 5

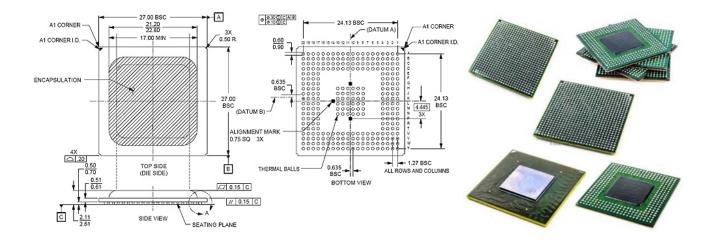

### **Ball Grid Array**

| Device                     | Aperture Length<br>(Ratio to pad) | Aperture Width<br>(Ratio to pad) | Comments                                                                     | Stencil<br>Thick. |

|----------------------------|-----------------------------------|----------------------------------|------------------------------------------------------------------------------|-------------------|

| PBGA / CBGA<br>(> 39.4mil) |                                   | 16 mil min                       | Square round<br>recommended<br>(keep the pad within<br>the solder mask area) | 6 mil             |

| PBGA<br>(= 39.4 mil)       |                                   | 16 mil to 25 mil                 | Square round<br>recommended<br>(keep the pad within<br>the solder mask area) | 6mil              |

| µBGA<br>(31.5 mil pitch)   |                                   | 16 mil to 18 mil                 | Square round<br>recommended<br>(keep the pad within<br>the solder mask area) | 5mil              |

| µBGA<br>(20 mil pitch)     |                                   | 11 mil square round              | Square round<br>recommended                                                  | 4mil              |

| µBGA<br>(16 mil pitch)     |                                   | 9 mil square round               | Square round recommended                                                     | 3, 4mil           |

| µBGA<br>(12 mil pitch)     |                                   | 7 mil square round               | Square round recommended                                                     | 3mil              |

It is very important to choose the correct foil thickness and design the proper pad size. Overprint the micro BGA to get the correct aspect ratio.

Note: if there are no solder resist, more reduction may required.

Stencil Design Guidelines

DOC#: 010

REV: 1 PAGE: 3 OF 5

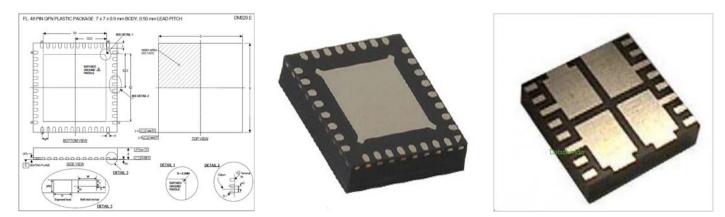

### Leadless packages

| Device                                           | Aperture LengthAperture Width(Ratio to pad)(Ratio to pad)                                                                                                | Comments                                                 | Stencil<br>Thick. |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------|

| 16 mil QFN (Quad -<br>Flat-No leads)             | Check for solder mask resist and apply reduction accordingly. 7 to 8 mil pad width. Overprint the signal pins or shift by 3-5 mil depends on the length. |                                                          | 3,4               |

| 20 mil QFN (Quad -<br>Flat-No leads)             | Check for solder mask resist and apply reduction accordingly. 8 to11 mil pad width. Overprint the signal pins or shift by 3-5 mil depends on the length. |                                                          | 4 Mil             |

| 25 mil QFN (Quad -<br>Flat-No leads)             | Check for solder mask resist and apply reduction accordingly. 8 to12 mil pad width. Overprint the signal pins or shift by 3-5 mil depends on the length. |                                                          | 4,5 mil           |

| 31 mil QFN (Quad -<br>Flat-No leads)             | 8 to16 mil pad width. Overprint the signal pins or shift by 3-5 mil depends on the length.                                                               |                                                          | 4,5 mil           |

| Ground pads (i.e.<br>under DFN,QFP,<br>QFN, etc) | 50-60% Area Reduction OR 40% X/Y reduction and window pane if necessary. Check if there are open via. If so avoid depositing solder on top of the vias.  | Recommend to close<br>the vias before<br>applying solder |                   |

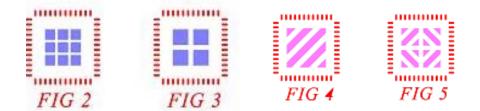

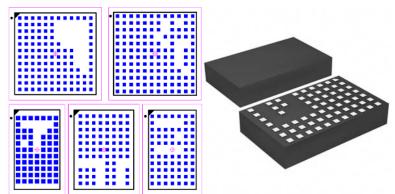

### Ground pad designs:

**Stencil Design Guidelines**

DOC#: 010

REV: 1 PAGE: 4 OF 5

### Line Grid Array

| Device           |                                                                         | Comments | Stencil<br>Thick. |

|------------------|-------------------------------------------------------------------------|----------|-------------------|

| LGA 50 MIL PITCH | 29 Mil with square round radius 3 mil, (SHOULD NOT EXCEED SOLDER MASK)  |          | 5 Mil             |

| LGA 40 MIL PITCH | 23 Mil with square round radius 3 mil, (SHOULD NOT EXCEED SOLDER MASK)  |          | 5 Mil             |

| LGA 31 MIL PITCH | 17 to 19 Mil square round radius 2 mil, (SHOULD NOT EXCEED SOLDER MASK) |          | 5 Mil             |

Note: Lower thickness is not recommended due to low standoff of the component. And thicker metal is not recommended due to too much flux to burn off and out gassing issues. Try to see what is recommended by the part manufacture.

**Stencil Design Guidelines**

DOC#: 010

REV: 1 PAGE: 5 OF 5

#### Chip components

Table 2

| Device               | Aperture Length<br>(Ratio to pad) | Aperture Width<br>(Ratio to pad) | Comments                                                                                                 | Stencil<br>Thick. |

|----------------------|-----------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------|-------------------|

| 1005                 | 1:1 OR<br>8 mil min pas size      | 1:1 OR<br>8 mil min pad size     | 0.2 mm gap between pads.                                                                                 | 3,4               |

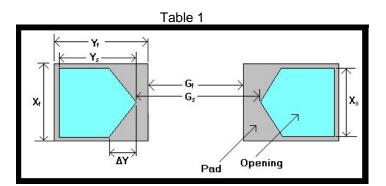

| 0201                 | 0.5 mil all around reduction      | 0.5 mil all around reduction     | 0.28 mm gap between pads. 1/5 home plates for NO clean process. (Table 1)                                | 4                 |

| 0402                 | 1 mil all around reduction        | 1 mil all around reduction       | Min gap of 15 mil between pads, ¼ home plates recommended for no clean process.                          | 5                 |

| 0603, 0805           | 5-10% reduction                   | 5-10% reduction                  | 1/3 home plate for NO clean leaded.<br>30/40/30 inverse home plates for NO clean<br>lead free. (Table 2) | 5,6               |

| 1205, 1210           | 5% reduction                      | 5% reduction                     | 1/4 Home plates for NO clean leaded,<br>30/40/30 inverse home places for No clean<br>lead free (Table 2) | 5,6               |

| Tantalum capacitors, | 1:1                               | 1:1                              | Overprint the pads by 5-10% if possible                                                                  | 5,6               |

| MELF<br>C-Shape Pad  | 1:1                               | 1:1                              | U – shape with 30/40/30. This will avoid component being roll over.                                      | 5,6               |

We recommend to do either home plate or radius inverted home plates to avoid mid chip solder balls or too much paste between the pads. Depends on the process and the foil thickness a 5%- 10% reduction is also recommended from the pad layout. Make sure the paste file is overlaid against the copper to see if there is any discrepancy between paste and copper layers. Some board shop tends to reduce the pads from copper and create the paste layers.