### INDIUM CORPORATION TECHNICAL PAPER

# Does Thermal Cycling Impact the Electrical Reliability of a No-Clean Solder Paste Flux Residue

Authored by: Eric Bastow, Indium Corporation.

#### Introduction

No-clean solder pastes are widely used in a number of applications that are exposed to wide variations in temperature during the life of the assembled electronics device. Some have observed that cracks can and do form in flux residue and have postulated that this is the result of or exacerbated by temperature cycling. Furthermore, the potential exists for the flux residue to soften or liquefy at elevated temperatures, and even flow if orientated parallel to gravity. In situations such as in automotive electronics, where significant temperature cycling is a reality and high reliability is a must, concern sometimes exists that the cracking and possible softening or liquefying of the residue may have a deleterious effect on the electrical reliability of the flux residue. This paper will attempt to address this concern.

For this work, two commercially available SAC305 Type 4 no-clean solder pastes, one halogen-free (ROL0) and the other halogencontaining (ROL1), will be examined. In accordance with IPC J-STD-004B, these solder pastes will be printed and reflowed, using the same common air reflow profile, on to IPC-B-24 SIR test boards. After reflow, each solder paste will have boards set aside for constant room temperature exposure, -40°C to +125°C temperature cycling, and -55°C to +175°C temperature cycling. For the two temperature cycling scenarios, boards will be orientated both perpendicular and parallel to gravity in the temperature cycling chamber. Upon completion of the temperature cycling, the boards will be submitted to Surface Insulation Resistance (SIR) testing per IPC-TM-650 2.6.3.7. The SIR readings will be plotted for each scenario and compared.

Please note that this work will focus on the cumulative effects of temperature cycling. This experiment does not attempt to look at the effects of temperature cycling in situ.

Table 1 shows the matrix of boards prepared and tested. All boards were prepared in accordance with IPC-TM-650 2.6.3.3. Two boards were prepared for each paste per scenario, as well as two boards per paste that saw no temperature cycling. The boards that were not temperature cycled were prepared at the same time as the boards for temperature cycling, but were kept at room temperature. For each temperature cycling and solder paste scenario, two boards were prepared for horizontal orientation and two boards for vertical orientation inside the temperature cycling chamber. In addition, two bare (no solder paste) control boards that saw no temperature cycling were included.

#### **ERIC BASTOW**

Eric Bastow, Assistant Technical Manager, America's Region, supports Indium's full range of solder products for the electronics assembly, semiconductor packaging, and thermal management markets.

Eric is the Chair of the SMTA

Certification Committee and a

member of the IPC APEX Technical

Program Committee. He is an

SMTA-certified process engineer

(CSMTPE) and has earned his

Six Sigma Green Belt. He is also

a certified IPC-A-600 and 610D

Specialist.

email: ebastow@indium.com Full biography: www.indium.com/biographies

Form No. 99355 R0

From One Engineer To Another

Table 1. SIR Test Matrix

| SIR Test Matrix           |                     |                     |                 |                 |                 |  |  |

|---------------------------|---------------------|---------------------|-----------------|-----------------|-----------------|--|--|

|                           | Temperature Cycling |                     |                 |                 |                 |  |  |

|                           |                     | Chamber Orientation |                 |                 |                 |  |  |

|                           |                     | Horizontal          |                 | Vertical        |                 |  |  |

| Solder Paste              | None                | -40°C to +125°C     | -55°C to +175°C | -40°C to +125°C | -55°C to +175°C |  |  |

| Halogen-Free (ROLO)       | 2                   | 2                   | 2               | 2               | 2               |  |  |

| Halogen-Containing (ROL1) | 2                   | 2                   | 2               | 2               | 2               |  |  |

| Controls                  | 2                   |                     |                 |                 |                 |  |  |

| Total                     | 22                  |                     |                 |                 |                 |  |  |

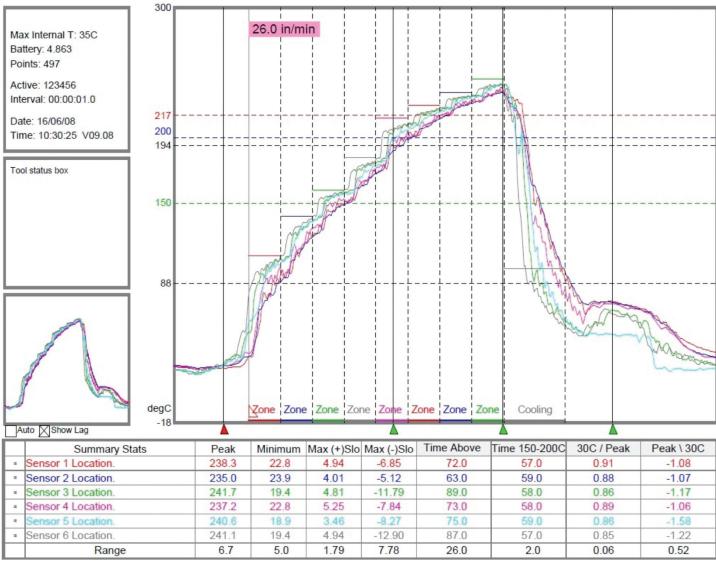

Figure 1 shows the air reflow profile that was used to reflow all the boards. (Control boards were not reflowed.)

Figure 1. Air reflow profile.

©2017 Indium Corporation

9

### INDIUM CORPORATION TECHNICAL PAPER INDIUM CORPORATION

As mentioned previously, two temperature cycling conditions were used: -40°C to +125°C and -55°C to +175°C. Table 2 shows the approximate dwell times and number of cycles completed. The boards were in the temperature cycling chambers for ~13 days. For the -55°C to 175°C temperature cycling condition, the boards saw ~535 cycles. For the -40°C to 125°C temperature cycling condition, the boards saw ~153 cycles.

Table 2. Temperature Cycling Parameters

| Temperature Cycling Parameters |                 |                  |  |  |  |

|--------------------------------|-----------------|------------------|--|--|--|

| Profile                        | Dwell (Minutes) | Cycles Completed |  |  |  |

| -40°C to +125°C                | 5               | ~153             |  |  |  |

| -55°C to +175°C                | 10              | ~535             |  |  |  |

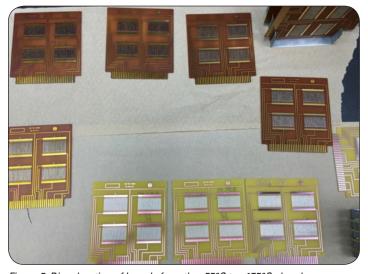

Figure 2 shows the orientation of the boards in the -40°C to +125°C chamber as photographed at the completion of the temperature cycling. The vertically-orientated boards can be seen in the metal rack on the left. The rack was orientated so that the flow of air could pass between the boards.

Figure 2. Orientation of the boards in the -40°C to +125°C chamber.

Figure 3 shows the orientation of the boards in the -55°C to +175°C chamber as photographed at the completion of the temperature cycling. The vertically-orientated boards can be seen in the metal rack on the left. The rack was orientated so that the flow of air could pass between the boards.

Figure 3. Orientation of the boards in the -55°C to +175°C chamber.

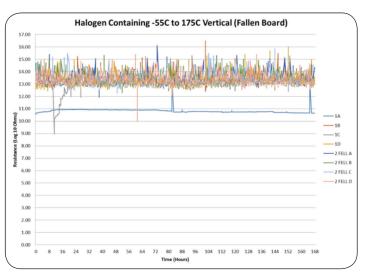

It was observed that the metal rack and vertically-orientated boards had been disturbed inside the chamber during the temperature cycling (see Figure 4). When and how this happened is unknown. One board had fallen out of the rack and was lying horizontally on the metal grill below. This board was labeled so that it could be identified as the fallen board.

The boards that underwent the -55°C to +175°C temperature cycling had darkened considerably compared to the boards from the -40°C to +125°C chamber (see Figure 5). However, other than the discoloration, there appeared to be no damage to the boards.

Figure 4. Disturbed verticallyorientated boards in the -55°C to +175°C chamber.

Figure 5. Discoloration of boards from the -55°C to +175°C chamber.

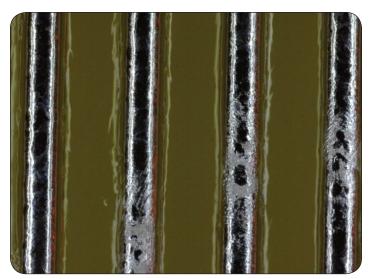

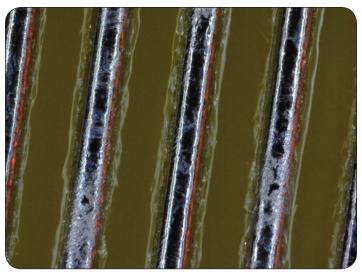

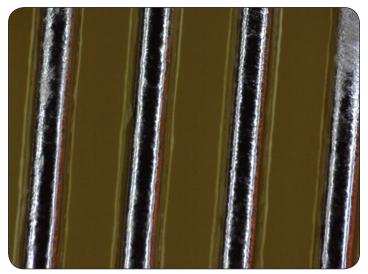

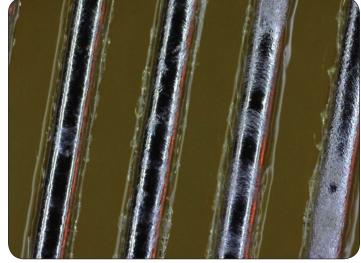

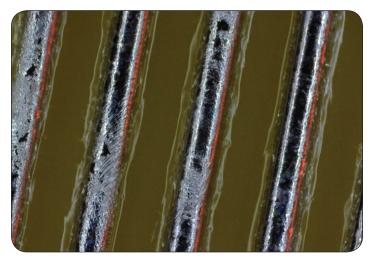

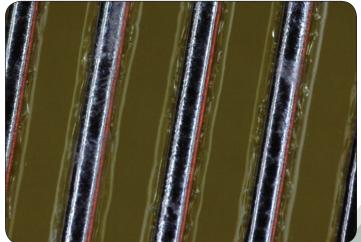

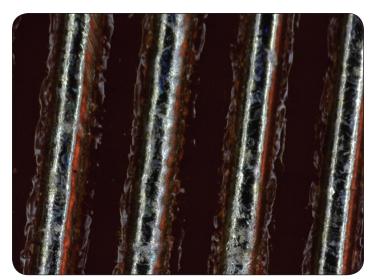

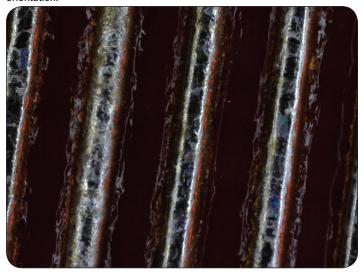

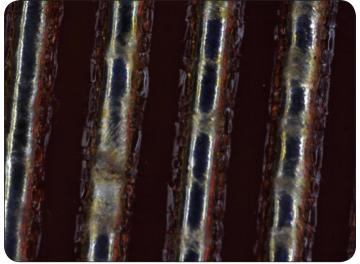

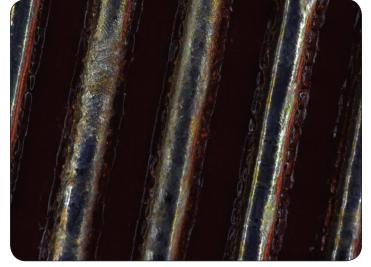

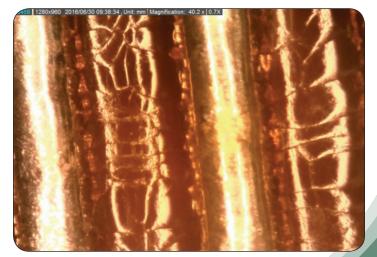

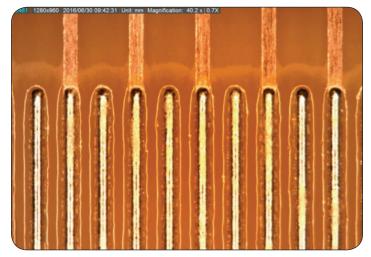

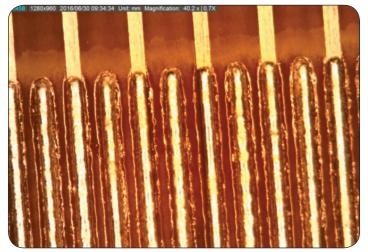

After temperature cycling and prior to SIR testing, the boards were examined for cracking in the flux residue. This is because some in the industry have either experienced or postulated cracking of the flux residue due to temperature cycling. Furthermore, it is said that this cracking in the residue can compromise the electrical reliability of the flux residue. Figures 6 through 15 are photographs of the flux residue on the SIR patterns under magnification.

3

## INDIUM CORPORATION TECHNICAL PAPER INDIUM

Figure 6. Halogen-free, no thermal cycling.

Figure 9. Halogen-free, -40°C to +125°C thermal cycling, vertical orientation.

Figure 7. Halogen-containing, no thermal cycling.

Figure 10. Halogen-containing, -40°C to +125°C thermal cycling, horizontal orientation.

Figure 8. Halogen-free, -40°C to +125°C thermal cycling, horizontal orientation.

Figure 11. Halogen-containing, -40°C to +125°C thermal cycling, vertical orientation.

1

# INDIUM CORPORATION TECHNICAL PAPER INDIUM.

Figure 12. Halogen-free, -55°C to +175°C thermal cycling, horizontal orientation.

Figure 13. Halogen-free, -55°C to +175°C thermal cycling, vertical orientation.

It was possible to capture a better image of what the cracking looks like in the samples that were cycled -55°C to +175°C (see Figure 16) by using a different microscope with different lighting.

It is important to note that the boards from the -55°C to +175°C temperature cycling chamber were at nearly room temperature when removed from the thermal cycling chamber. The boards from the -40°C to +125°C temperature cycling chamber were toward the cooler end of the cycle when they were removed. All of the boards that were temperature cycled show some amount of cracking in the flux residue, especially where it is in direct contact with the solder. It is the author's belief that at elevated temperatures above the softening point of the rosin, these cracks may "heal" and then not re-form until the cycle swings below the softening point of the rosin. It is said that cracks negatively

Figure 14. Halogen-containing, -55°C to +175°C thermal cycling, horizontal orientation.

Figure 15. Halogen-containing, -55°C to +175°C thermal cycling, vertical orientation.

Figure 16. Flux cracking, -55°C to 175°C thermal cycling.

5

### INDIUM CORPORATION TECHNICAL PAPER INDIUM CORPORATION

impact the SIR performance of a flux residue. Those negative effects, should they be real, should be captured in this experiment.

There was some flow of the flux, although it would probably be better to refer to it as flux "creep" or flux "migration" because it was much less dramatic than the author expected. The degree of migration was only present, to any appreciable extent, with the halogen-free solder paste. The flux migration did not seem to be sensitive to the orientation of the board as it may be more of a wicking or wetting phenomenon, as opposed to a gravity-induced phenomenon. Perhaps, if more flux residue were present, gravity-induced flow may become more apparent. Figures 17 and 18 show the flux migration from -40°C to +125°C and -55°C to +175°C respectively.

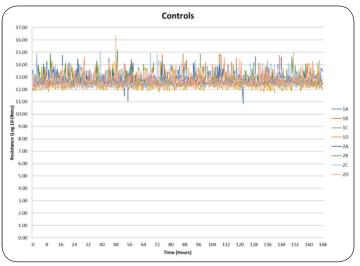

After the boards were photographed, they were submitted to SIR testing per J-STD-004B, which references IPC-TM-650 2.6.3.7. The chamber conditions are 90% RH and 40°C. A DC electrical bias is applied to produce a field strength of 25+/- 1 V/mm between adjacent parallel traces. Assuming that the surface insulation resistance is greater than 1 M $\Omega$ , this field strength corresponds to an applied voltage of 5+/- 0.2V for 0.008" (200 $\mu$ ) spacing. A measurement is made at least once every 20 minutes for a duration of 168 hours (7 days or 1 week). All measurements after 24 hours must be 100M $\Omega$  or greater to constitute a "pass" per J-STD-004B – Amendment 1.

Figure 17. Flux migration, -40°C to +125°C.

Figure 18. Flux migration, -55°C to +175°C.

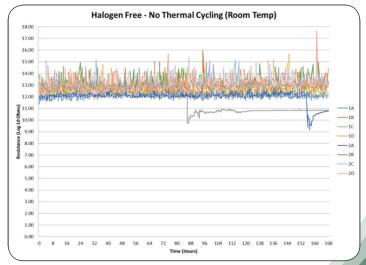

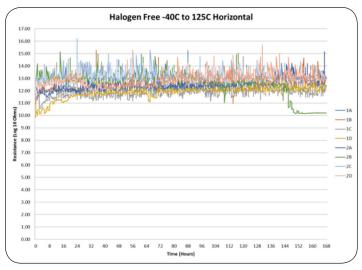

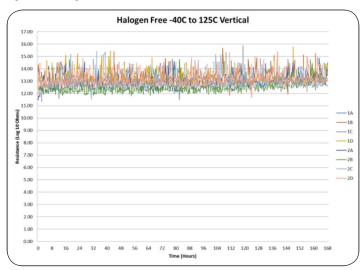

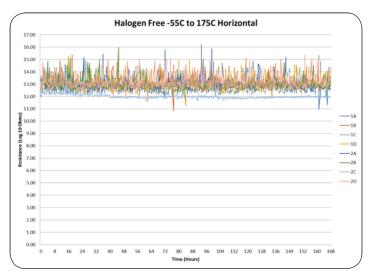

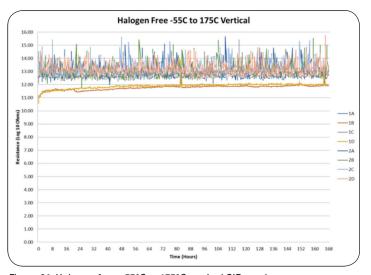

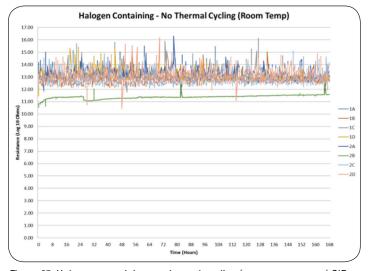

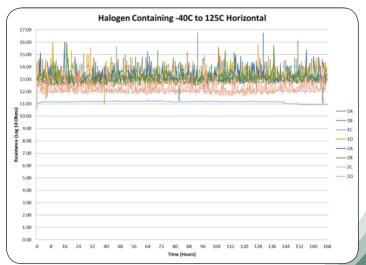

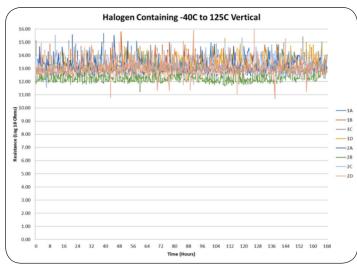

Figures 19 through 29 show the SIR results for each scenario.

Figure 19. Controls SIR results.

Figure 20. Halogen-free, no thermal cycling (room temperature) SIR results.

6

# INDIUM CORPORATION TECHNICAL PAPER INDIUM CORPORATION

Figure 21. Halogen-free, -40°C to 125°C horizontal SIR results.

Figure 22. Halogen-free, -40°C to 125°C vertical SIR results.

Figure 23. Halogen-free, -55°C to 175°C horizontal SIR results.

Figure 24. Halogen-free, -55°C to 175°C vertical SIR results.

Figure 25. Halogen-containing, no thermal cycling (room temperature) SIR results.

Figure 26. Halogen-containing, -40°C to 125°C horizontal SIR results.

7

### INDIUM CORPORATION TECHNICAL PAPER INDIUM CORPORATION

Figure 27. Halogen-containing, -40°C to -125°C vertical SIR results.

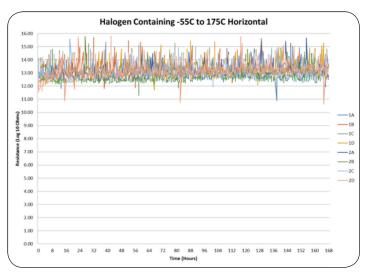

Figure 28. Halogen-containing, -55°C to 175°C horizontal SIR results.

Figure 29. Halogen-containing, -55°C to 175°C vertical (with fallen board) SIR results.

After critical examination of Figures 19 through 29, we can clearly see that all SIR values exceed the minimum J-STD-004B value of 1 x 108 Ohms and the lowest value achieved was 1 x 108.96 Ohms, nearly one order of magnitude higher than the minimum J-STD-004B value of 1 x 108 Ohms (see Pattern 1C of Figure 29 at  $\sim$  11 hours).

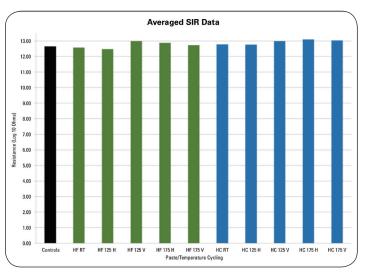

For ease of comparison and to detect any meaningful trend in the SIR data, the values for each scenario were averaged and then placed in a single graph, side by side (see Figure 30). It can be argued that averaging SIR data is not wise. However, the emphasis of this paper is to look at the general effect of temperature cycling, and not meant to be a point by point analysis of the SIR values.

Figure 30. Averaged SIR results.

Key for Figure 30:

- HF = Halogen-free solder paste

- HC = Halogen-containing solder paste

- RT = Room temperature no thermal cycling

- 125 = -40°C to 125°C thermal cycling

- 175 = -55°C to 175°C thermal cycling

- H = Horizontal orientation during thermal cycling

- V = Vertical orientation during thermal cycling

A few things are immediately evident when viewing the data this way:

- 1) The averaged SIR values of all scenarios are virtually identical.

- 2) The averaged SIR values of the temperature cycled pastes are virtually identical to their respective room temperature scenarios.

8

- 3) All of the scenarios produced average SIR values that are comparable to or higher than the controls.

- 4) All of the averaged SIR values are at least 4 orders or magnitude higher than the minimum J-STD-004B requirement of 1 x 108 Ohms.

- 5) There is no meaningful difference between how the halogenfree and halogen-containing solder paste formulations respond to temperature cycling.

- 6) The orientation of the boards, horizontal and vertical, did not have any impact on the SIR values.

- 7) The number of cycles and range of the temperature cycling has no meaningful impact on the averaged SIR values.

- 8) Even with the inclusion of (a) pattern(s) that exhibited noticeably lower values than the rest of the patterns for a given scenario, the impact to the average was minimal.

These results are no surprise to the author. Knowing that both of these temperature cycling regimes are likely high enough to soften or even liquefy the flux residue, it is the author's belief that each time the residue experienced the hot side of the cycle, the cracks would have the opportunity to "heal" and re-encapsulate. Therefore, the exposure of the residual activators and activator/ metal oxide by-products in the flux residue caused by the cracking either does not really happen to any significant degree or the residue readily re-encapsulates them. It would be interesting to know if the cracking in the residue is the result of CTE mismatch between the various materials in and on the SIR board, or that the residue is simply drying and/or burning off and reducing in volume, or some combination of both.

Orientating the boards so that they were parallel to gravity did not seem to cause any substantial "flow" of the flux residue when the thermal cycle exceeded the softening point of the rosin. Any "flow" that did occur seemed to be more of a wetting or wicking action of the flux across the surface of the board. Keep in mind that there is no solder mask on the SIR test boards—they are bare FR4.

The results of this experiment suggest that thermal cycling and the resulting cracks that form in the flux residue pose no deleterious threat to the electrical reliability of a ROL0 or ROL1 flux residue.

First presented at APEX 2017, February 2017, San Diego, California.